# スイッチングアンプ

## 特徴

- 低コストのインテリジェント・スイッチング・アンプ

- ほとんどの組み込みマイコンやデジタルシグナルコントローラに直接接 続可能

- デッドタイム生成機能とシュートスルー防止機能を備えたゲートドライ バロジックを内蔵

- 広い電源電圧範囲 (8.5 V~60 V)

- 各相のピーク出力電流が10A以上

- 各出力の独立した電流検出

- ユーザープログラム可能なサイクル毎の電流制限保護

- 過電流および温度超過警告信号

- 双方向DCブラシモーター

- 2個の一方向性DCブラシ・モーター

- 2個の独立したソレノイドアクチュエーター

- ステッピングモーター

## 説明

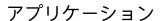

SA53は、主にDCブラシモーターを駆動するために設計された、完全一体型のスイッチングアンプです。2つの独立したハーフブリッジにより、マイコンまたはDSCの制御下で10アンペア以上のピーク出力電流を実現しています。また、熱および短絡の監視機能を備えており、マイクロコントローラが適切な処置を行うための障害信号を生成します。

さらに、サイクルごとの電流制限により、マイクロコントローラーに依存しない、ユーザーがプログラム可能なハードウェア保護を実現しています。出力電流は、革新的な低損失技術を用いて測定されます。SA53は、CMOSロジック制御とコンプリメンタリーDMOS出力パワーデバイスを同一IC上で実現するマルチテクノロジープロセスを採用しています。また、PチャネルハイサイドFETを使用することで、ブートストラップやチャージポンプ回路なしで60V動作が可能です。

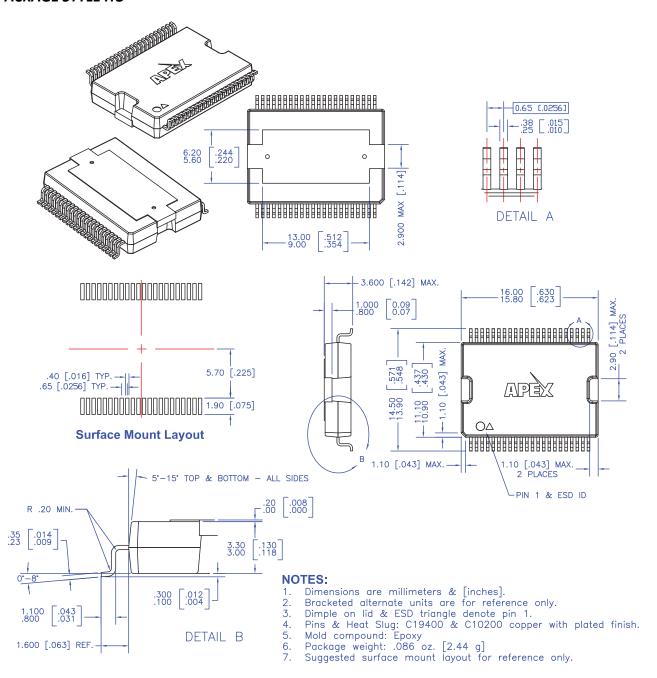

HSOP表面実装パッケージは、優れた熱性能と低背表面実装パッケージの利点をバランスよく兼ね備えています。

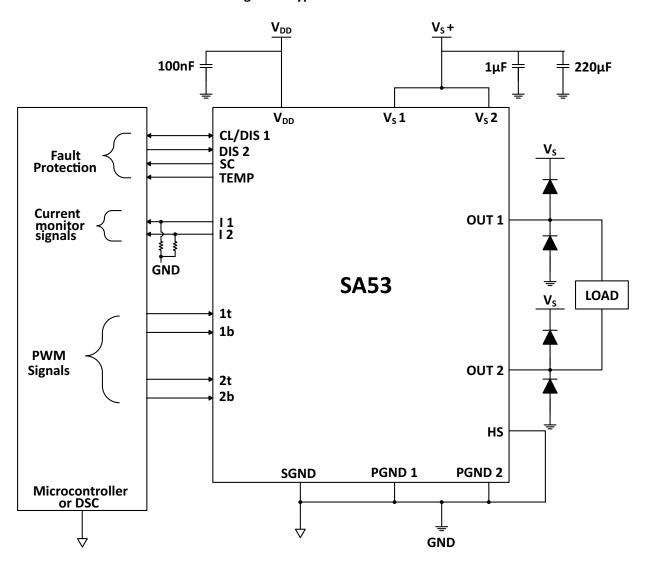

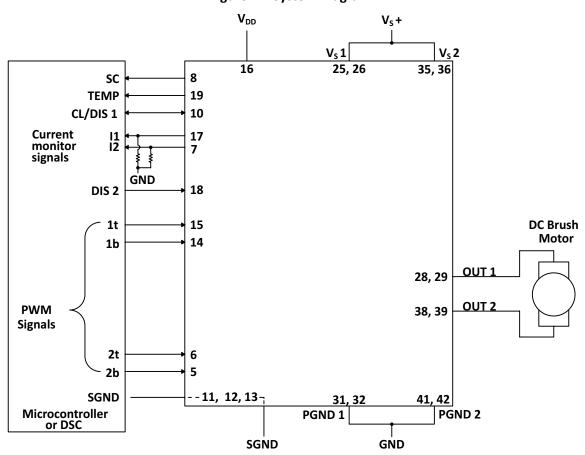

# 典型的な接続

**Figure 2: Typical Connection**

# ピンアウトと説明のテーブル

**Figure 3: External Connections**

| _1_ | NC ⊲            |                     | HS                | 44 |

|-----|-----------------|---------------------|-------------------|----|

| _2  | NC              |                     | NC                | 43 |

| _3_ | NC              |                     | PGND 2            | 42 |

| _4_ | NC              |                     | PGND 2            | 41 |

| _5  | 2b              |                     | NC                | 40 |

| _6  | 2t              |                     | OUT 2             | 39 |

| _7_ | 12              |                     | OUT 2             | 38 |

| 8   | sc              |                     | NC                | 37 |

| 9   | SGND            |                     | V <sub>s</sub> _2 | 36 |

| 10  | CL/DIS1         | CAEO                | V <sub>s</sub> _2 | 35 |

| 11  | SGND            | SA53                | NC                | 34 |

| 12  | SGND            | (Bottom View,       | NC                | 33 |

| 13  | SGND            | opposite heat slug) | PGND 1            | 32 |

| 14  |                 |                     | PGND 1            | 31 |

| 15  | 1b<br>1t        |                     | NC                | 30 |

|     | V <sub>DD</sub> |                     | OUT 1             | 29 |

| 17  | I 1             |                     | OUT 1             | 28 |

| 18  | DIS2            |                     | NC NC             | 27 |

| 19  |                 |                     | V <sub>s</sub> _1 | 26 |

| 20  | TEMP<br>NC      |                     | V <sub>S</sub> _1 | 25 |

| 21  | NC<br>NC        |                     | NC                | 24 |

| 22  | NC              |                     | HS                | 23 |

|     |                 |                     |                   | ,  |

ケースはピン23と44に接続されています。ケースに電流を流してはいけません。電源のバイパス処理が必要です。

| Pin Number    | Name    | Description                                                                                                                                                                                    |  |  |

|---------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 5             | 2b      | Logic high commands phase 2 lower (bottom) FET to turn on.                                                                                                                                     |  |  |

| 6             | 2t      | Logic high commands phase 2 upper (top) FET to turn on.                                                                                                                                        |  |  |

| 7             | 12      | Phase 2 current sense output. Outputs a current proportional to I <sub>D</sub> of the upper (top) FET of channel 2. Connect to a sense resistor to SGND to monitor current.                    |  |  |

| 8             | SC      | Short circuit output. When a short circuit condition is experienced on either channel, this pin will go high for 200ns. This does not disable the outputs.                                     |  |  |

| 9, 11, 12, 13 | SGND    | Signal ground. Reference all logic circuitry to these pins. Connect to PGND 1 and PGND 2 as close to the amplifier as possible.                                                                |  |  |

| 10            | CL/DIS1 | Logic high places both outputs in a high impedance state. Pulling to logic low disables cycle-by-cycle current limit. If unconnected, cycle-by-cycle current limit will be allowed to operate. |  |  |

| 14            | 1b      | Logic high commands phase 1 lower (bottom) FET to turn on.                                                                                                                                     |  |  |

| 15            | 1t      | Logic high commands phase 1 upper (top) FET to turn on.                                                                                                                                        |  |  |

| 16 Vdd        |         | Voltage supply for logic circuit. Connect 5 V supply. The ground terminal of the supply must be connected to SGND.                                                                             |  |  |

| Pin Number | Name   | Description                                                                                                                                                                 |

|------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 17         | l 1    | Phase 1 current sense output. Outputs a current proportional to I <sub>D</sub> of the upper (top) FET of channel 1. Connect to a sense resistor to SGND to monitor current. |

| 18         | DIS2   | Logic high places both outputs in a high impedance state. This pin may be left unconnected.                                                                                 |

| 19         | TEMP   | This pin will go logic high when the die temperature reaches 135°C. This does not disable the outputs.                                                                      |

| 23, 44     | HS     | These pins are internally connected to the heat slug. Connect to PGND. Neither the heatslug nor these pins should carry current.                                            |

| 25, 26     | Vs 1   | Voltage supply for channel 1.                                                                                                                                               |

| 28, 29     | OUT 1  | The output connection for channel 1.                                                                                                                                        |

| 31, 32     | PGND 1 | Power ground. These pins are directly connected to the bottom FET of channel 1. Connect to SGND and PGND 2 as close to the amplifier as possible.                           |

| 35, 36     | Vs 2   | Voltage supply for channel 2.                                                                                                                                               |

| 38, 39     | OUT 2  | The output connection for channel 2.                                                                                                                                        |

| 41, 42     | PGND 2 | Power ground. These pins are directly connected to the bottom FET of channel 2. Connect to SGND and PGND 1 as close to the amplifier as possible.                           |

| All Others | NC     | No connection.                                                                                                                                                              |

## 端子説明

**VS:** 出力トランジスタ用の電源電圧。これらの端子は、PGND端子とデカップリング(高周波特性の良い1µFのコンデンサを推奨)する必要があります。デカップリングコンデンサは、できるだけVS端子とPGND端子の近くに設置してください。VS端子には、負荷電流のピークやモーターの回転に対応するため、追加の容量が必要です。

負荷電流のピークやモーターの回生に対応するため、VS端子に追加の容量が必要となります。バイパスコンデンサの選択については、本データシートのアプリケーションの項を参照してください。VSピン25-26はフェーズ1の供給電流のみを流すことに注意してください。ピン35-36はフェーズ2の電源電流を供給します。第1相は第2相とは異なる電源電圧で動作することができます。両方のVS電圧は、低電圧状態を監視します。

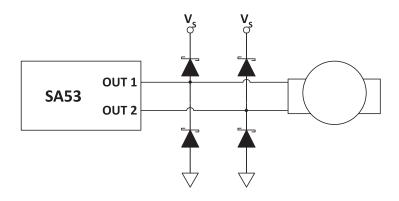

OUT 1, OUT 2: これらのピンは、負荷への電源出力接続です。注: 誘導負荷を駆動する場合は、スイッチング特性の良い(高速の tRR 仕様)ショットキーダイオードを 2 個ずつ接続し、出力 FET の寄生バックボディダイオードと並列になるようにすることを推奨します。

PGND: パワーグラウンド。出力FETのグランドリターン接続です。負荷からのリターン電流はこの端子に流れます。 PGNDは内部で数Ωの抵抗を介してSGNDに接続されています。詳細は 詳細は、本データシートの2.1項を参照してください。

SC: ショートサーキット出力。入力されたコマンドに従わない状態が出力に検出されると 短絡状態であることを示し、SC端子がHになります。SC信号はスイッチング遷移中に約200nsブランクになります。切り替え時には約200nsのブランクが発生しますが、大電流アプリケーションでは、SC端子に短いグリッチが現れることがあります。SC端子に現れることがあります。SC出力がHIGHになっても、自動的にデバイスがディセーブルになることはありません。SC端子にはには12kΩの直列抵抗が内蔵されています。

**1b, 2b:** これらのシュミットトリガーによるロジックレベル入力は、関連する最下段、つまり下側のNチャンネル出力 FETをオン/オフする役割を果たします。ロジックHighで下側のNch FETがONとなり、ロジックLowで下側のNch FET がOFFとなります。対応する1tまたは2t入力がハイであると同時に1bまたは2bがハイである場合、保護回路はその出力 フェーズでのシュートスルーを防止するために両方のFETをオフにします。また、保護回路には、上下の入力信号が同時に切り替わった場合に、出力にデッドタイムを挿入するデッドタイムジェネレータも含まれています。

**1t, 2t:** これらのシュミットトリガーによるロジックレベル入力は、関連する上側(upperPchannel FET)の出力をオン/オフする役割を果たします。ロジックHighで上側のPchannel FETがONになり、ロジックLowで上側のPchannel FETがOFFになります。

**11, I2:** 電流センス端子。SA53は,この端子に,その相のトップ側PチャネルFETに流れる電流に比例した正の電流を供給する。PチャンネルFETのバックボディダイオードや外部のショットキーダイオードを介して流れる整流電流は、電流センス端子には登録されません。また,ローサイドのNチャネルFETを流れる電流は,いずれの方向にも電流検出端子には登録されません。電流センス端子からSGNDに接続された抵抗器は、位相電流を表す電圧信号を生成し、プロセッサのADC入力や外部回路でモニターすることができます。プロセッサーのADC入力や外部回路でモニターすることができます。

また、電流センス端子は、電流制限の閾値となる電圧基準Vthと内部で比較されます。いずれかの電流センスピンの電圧がVthを超えた場合、サイクルごとの電流制限回路が動作します。この機能の詳細は、本データシートのアプリケーションの項に記載されています。

CL/DIS1: SA53のディセーブル回路に直接接続されています。このピンをロジックHにすると、OUT1とOUT2がハイインピーダンス状態になります。また、この端子は、12kΩの抵抗を介して電流制限ラッチの出力に内部接続されており、サイクル毎の電流制限機能の動作を監視することができます。この端子をロジックLOWにすることで、サイクル毎の電流制限機能を効果的に無効にすることができます。リミット機能を無効にします。

SGND: ロジック電源端子VDDのグランドリターン接続です。すべての内部アナログおよびロジック すべての内部アナログおよびロジック回路は、この端子を基準にしている。PGNDは内部で数Ωの抵抗を介してGNDに接続されています。OMS しかし、デバイスのできるだけ近くで、GNDピンとPGNDピンを外部で接続することを強くお勧めします。接続することをお勧めします。このようにしないと、立ち上がりや立ち下がりのエッジで出力端子が発振することがあります。エッジの立ち上がりや立ち下がり時に出力端子が発振することがあります。

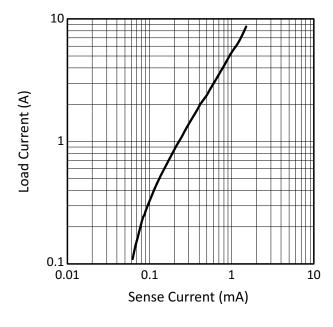

VDD: 5V電源の接続端子で、SA53のロジック回路やアナログ回路に電源を供給しています。この端子は、SGND端子にデカップリング(高周波特性の良い0.1µF以上のコンデンサを推奨)する必要があります。SGND端子にデカップリングすることをお勧めします。

DIS2: DIS2: 端子は、シュミットトリガによるロジックレベル入力で、HighにするとOUT1とOUT2がハイインピーダンスになります。ハイインピーダンス状態になります。DIS2には12k $\Omega$ のプルダウン抵抗が内蔵されていますので、未接続のままでも接続されていません。

**TEMP:** このロジックレベルの出力は、SA53のダイ温度が約135°Cに達したときにHighになります。この端子は、デバイスを自動的にディセーブルにすることはありません。この端子はデバイスを自動的にディセーブルすることはありません。

HS: これらのピンは、パッケージ裏面のサーマルスラッグに内部接続されています。GNDに接続してください。ヒートスラグやこれらの端子は、大電流を流すためには使用しないでください。

NC: これらの "ノーコネクト "ピンは、接続しないままにしておく必要があります。

## スペック

すべてのMin/Max特性および仕様は、指定された動作条件で保証されています。代表的な性能特性および仕様は、代表的な電源電圧および $TC=25^{\circ}C$ での測定から得られたものです。

### **ABSOLUTE MAXIMUM RATINGS**

| Parameter                                 | Symbol          | Min    | Max                    | Units |

|-------------------------------------------|-----------------|--------|------------------------|-------|

| Supply Voltage                            | V <sub>s</sub>  |        | 60                     | V     |

| Supply Voltage                            | V <sub>DD</sub> |        | 5.5                    | V     |

| Logic Input Voltage                       |                 | (-0.5) | (V <sub>DD</sub> +0.5) | V     |

| Output Current, peak, 10ms <sup>1</sup>   | I <sub>O</sub>  |        | 10                     | А     |

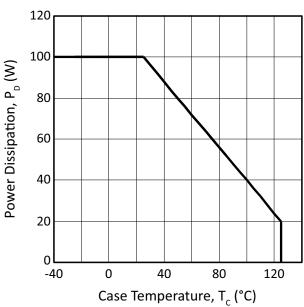

| Power Dissipation, avg. 25°C <sup>1</sup> | P <sub>D</sub>  |        | 100                    | W     |

| Temperature, pin solder, 10s max.         |                 |        | 260                    | °C    |

| Temperature, junction <sup>1</sup>        | T <sub>J</sub>  |        | 150                    | °C    |

| Temperature Range, storage                |                 | -65    | +125                   | °C    |

| Operating Temperature Range, case         | T <sub>C</sub>  | -25    | +85                    | °C    |

<sup>1.</sup> 高温環境下での長期使用は製品寿命を縮める原因となります。高いMTBFを実現するためには、内部の電力消費を抑える必要があります。

#### **LOGIC**

| Parameter                          | Test Conditions | Min | Тур | Max | Units |

|------------------------------------|-----------------|-----|-----|-----|-------|

| Input Low                          |                 |     |     | 1   | V     |

| Input High                         |                 | 1.8 |     |     | V     |

| Output Low                         |                 |     |     | 0.3 | V     |

| Output High                        |                 | 3.7 |     |     | V     |

| Output Current (SC, Temp, CL/DIS1) |                 |     | 50  |     | mA    |

### **POWER SUPPLY**

| Parameter                                   | Test Conditions                                                                            | Min  | Тур | Max | Units |

|---------------------------------------------|--------------------------------------------------------------------------------------------|------|-----|-----|-------|

| V <sub>S</sub>                              |                                                                                            | UVLO | 50  | 60  | V     |

| V <sub>S</sub> Undervoltage Lockout, (UVLO) |                                                                                            |      | 8.3 |     | V     |

| V <sub>DD</sub>                             |                                                                                            | 4.5  |     | 5.5 | V     |

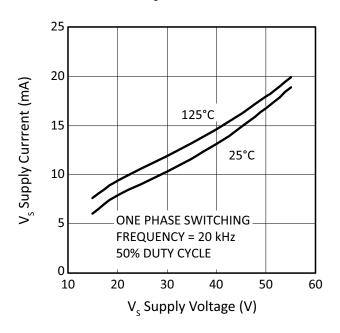

| Supply Current, V <sub>S</sub>              | 20 kHz (One phase switching at 50% duty cycle), V <sub>S</sub> =50V, V <sub>DD</sub> =5V   |      | 25  | 30  | mA    |

| Supply Current, V <sub>DD</sub>             | 20 kHz (One phase switching at 50% duty cycle), V <sub>S</sub> =50V, V <sub>DD</sub> =5.5V |      | 5   | 6.5 | mA    |

### **CURRENT LIMIT**

| Parameter                     | Test Conditions | Min | Тур  | Max | Units |

|-------------------------------|-----------------|-----|------|-----|-------|

| Current Limit Threshold (Vth) |                 |     | 3.75 |     | V     |

| Vth Hysteresis                |                 |     | 100  |     | mV    |

#### OUTPUT

| Parameter                          | Test Conditions       | Min | Тур | Max | Units |

|------------------------------------|-----------------------|-----|-----|-----|-------|

| Current, continuous                | 25°C Case Temperature | 3   |     |     | Α     |

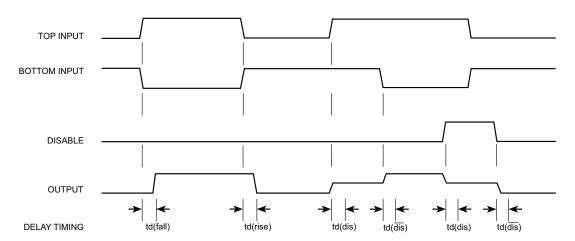

| Rising Delay, TD (rise)            | See Figure 20         |     | 270 |     | ns    |

| Falling Delay, TD (fall)           | See Figure 20         |     | 270 |     | ns    |

| Disable Delay, TD (dis)            | See Figure 20         |     | 200 |     | ns    |

| Enable Delay, TD ( <u>dis</u> )    | See Figure 20         |     | 200 |     | ns    |

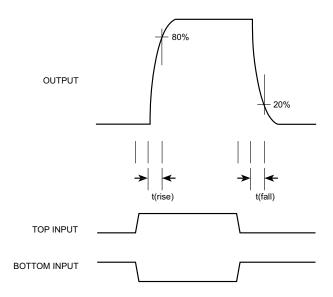

| Rise Time, t (rise)                | See Figure 21         |     | 50  |     | ns    |

| Fall Time, t (fall)                | See Figure 21         |     | 50  |     | ns    |

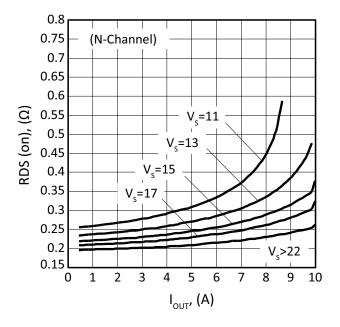

| On Resistance Sourcing (P-Channel) | 5A Load               |     | 400 |     | mΩ    |

| On Resistance Sinking (N-Channel)  | 5A Load               |     | 400 |     | mΩ    |

#### **THERMAL**

| Parameter                    | Test Conditions | Min | Тур  | Max | Units |

|------------------------------|-----------------|-----|------|-----|-------|

| Thermal Warning              |                 |     | 135  |     | °C    |

| Thermal Warning Hysteresis   |                 |     | 40   |     | °C    |

| Resistance, junction to case | Full temp range |     | 1.25 | 1.5 | °C/W  |

| Temperature Range, case      | Meets Specs     | -25 |      | +85 | °C    |

ノート:出力電流の定格は、デューティサイクル、周囲温度、ヒートシンクによって制限される場合があります。どのような条件であっても、指定された定格電流またはジャンクション温度150℃を超えないようにしてください。

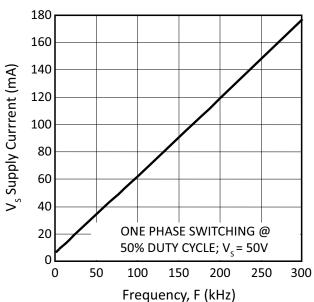

### **TYPICAL PERFORMANCE GRAPHS**

Figure 4: V<sub>s</sub> Supply Current

Figure 5: V<sub>s</sub> Supply Current

**Figure 6: Current Sense**

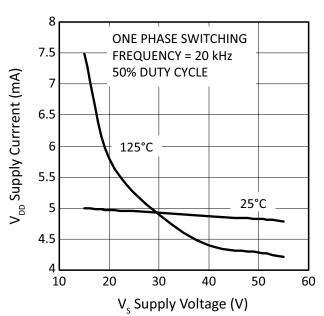

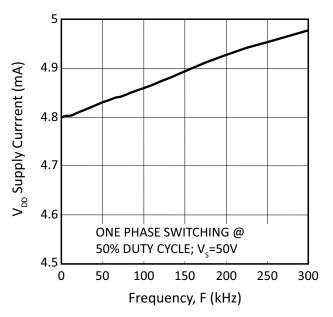

Figure 7: V<sub>DD</sub> Supply Current

Figure 8: V<sub>DD</sub> Supply Current

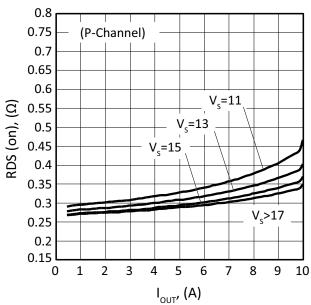

Figure 10: On Resistance - Bottom FET

**Figure 9: Power Derating**

Figure 11: On Resistance - Top FET

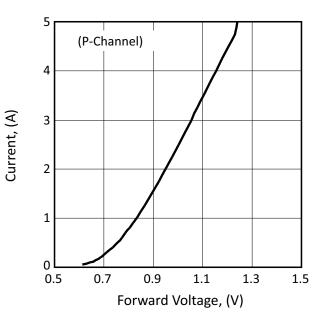

Figure 12: Diode Forward Voltage - Bottom FET

(N-Channel)

4

(N-Channel)

2

1

0.5

0.7

0.9

1.1

1.3

1.5

Forward Voltage, (V)

Figure 13: Diode Forward Voltage - Top FET

## 一般

安定性、供給、ヒートシンク、実装、電流制限、SOAの解釈、仕様の解釈などについて書かれたアプリケーションノート1「一般的な動作に関する注意事項」をお読みください。Apex Microtechnologyの完全なアプリケーションノートライブラリ、テクニカルセミナーワークブック、および評価キットについては、www.apexana-log.comをご覧ください。

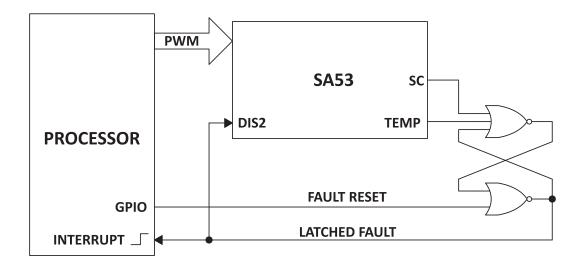

## SA53 操作方法

SA53は、主にDCブラシモーターを駆動するために設計されています。しかし、2つの高電流出力を必要とするあらゆるアプリケーションに使用することができます。SA53の信号セットは、DSPやマイクロコントローラーとのインターフェースに特化して設計されています。代表的なシステムブロック図を下図に示します。過熱、短絡、電流制限の各フォルト信号は、システムコントローラに重要なフィードバックを提供し、フォルト状態の場合に出力ドライバを安全に無効にすることができます。両相のハイサイド電流モニターは、トルクの調整や制限に使用できる性能情報を提供します。

Figure 14: System Diagram

図15のブロック図は、SA53の入力構造と出力構造の特徴を示している。簡単にするため、単相を示しています。

12k SC Current Sense SC Logic †| ||11 Temp Sense 12k TEMP Ref 12k 」Lim 1 CL/DIS 1 Lim 2 UVLO DIS 2 **∮ 12k**  $v_{\rm s}$ 1t Gate OUT 1 Control 1b SGND PGND

Figure 15: Input And Output Structures For A Single Phase Layout Considerations

#### **TRUTH TABLE**

| At, Bt,<br>Ct | Ab,<br>Bb, Cb | la, lb,<br>lc     | I <sub>LIM</sub> /<br>DIS1 | DIS2 | Out A, Out B, Out<br>C   | Comments                                                                                                                                                                     |

|---------------|---------------|-------------------|----------------------------|------|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0             | 0             | Х                 | Х                          | Х    | High-Z                   | Top and Bottom output FETs for that phase are turned off.                                                                                                                    |

| 0             | 1             | <v<sub>th</v<sub> | 0                          | 0    | PGND                     | Bottom output FET for that phase is turned on.                                                                                                                               |

| 1             | 0             | <v<sub>th</v<sub> | 0                          | 0    | VS                       | Top output FET for that phase is turned on.                                                                                                                                  |

| 1             | 1             | Х                 | Х                          | Х    | High-Z                   | Both output FETs for that phase are turned off.                                                                                                                              |

| Х             | Х             | >V <sub>th</sub>  | 1                          | Х    | High-Z                   | Voltage on Ia, Ib, or Ic has exceeded Vth, which causes I <sub>LIM</sub> /DIS1 to go high. This internally disables Top and Bottom output FETs for ALL phases.               |

| Х             | Х             | Х                 | Х                          | 1    | High-Z                   | DIS2 pin pulled high, which disables all outputs.                                                                                                                            |

| Х             | Х             | Х                 | Pulled<br>High             | Х    | High-Z                   | Pulling the I <sub>LIM</sub> /DIS1 pin high externally acts as a second disable input, which disables ALL output FETs.                                                       |

| Х             | Х             | Х                 | Pulled<br>Low              | 0    | Determined by PWM inputs | Pulling the I <sub>LIM</sub> /DIS1 pin low externally disables the cycle-by-cycle current limit function. The state of the outputs is strictly a function of the PWM inputs. |

| Х             | Х             | Х                 | Х                          | Х    | High-Z                   | If $V_S$ is below the UVLO threshold all output FETs will be disabled.                                                                                                       |

dV/dtやdI/dtが非常に高い信号を出力します。適切な配線と適切な電源のバイパス処理により、正常な動作が保証されます。不適切な配線やバイパス処理は、不安定で効率の悪い動作や、出力でのリンギングの原因となります。

VS電源は、VSピンにできるだけ近い場所に取り付けられた表面実装セラミックコンデンサでバイパスする必要があります。ロジックの制御信号にノイズが混入するのを防ぐため、コンデンサからVS端子、GND端子までの配線の総インダクタンスは最小限にしてください。SA53の近くには、出力電流1アンペアあたり25μF以上の低ESRコンデンサを配置する必要があります。コンデンサは、スイッチング用途に適したものを選んでください。

VDD電源のバイパス条件はそれほど厳しくはありませんが、それでも必要です。0.1µF~0.47µFの表面実装型セラミックコンデンサ(X7RまたはNPO)をVDDピンに直接接続すれば十分です。SGNDピンとPGNDピンは内部で接続されていますが、これらのピンは、小さな信号配線の寄生抵抗が十分な電圧降下を発生させ、誤って入力遷移を引き起こす可能性があるため、ロジックおよび信号グランドのトレースにモーター電流が流れないように外部で接続する必要があります。また、グランドプレーンを電源部とロジック部に分け、背中合わせのショットキーダイオードで接続する方法もあります。これにより、信号と電源のグランドトレース間のノイズを分離し、プレーンセクション間の大電流の通過を防ぐことができます。

信号間の誘導結合を最小にするために、上下のPCB平面上の未使用領域をソリッドまたはハッチの銅で埋める必要があります。この銅の充填は未接続のままでも構いませんが、グランドプレーンを設けることをお勧めします。

## 故障表示

過熱または短絡のいずれかの障害の場合、SA53は出力を無効にするアクションをとりません。代わりに、SC信号とTEMP信号が外部コントローラに供給され、適切な行動を決定することができます。ほとんどの場合、SCピンはプロセッサのFAULT入力に接続され、直ちにPWM出力が無効になります。一方、TEMP故障の場合はこのような即時性は必要なく、通常はプロセッサのGPIOまたはキーボード割り込みピンに接続されます。この場合、プロセッサはこの状態を外部からの割り込みとして認識し、割り込みサービスルーチンを介してソフトウェアで処理することができます。プロセッサはオプションとして、すべての入力をLowにするか、SA53のディセーブル入力のいずれかにHighレベルをアサートすることができます。

図16 は、フォルト表示に応じてすべての出力をハードウェアでシャットダウンする外付けSRフリップフロップを示しています。SC または TEMPフォルトによってラッチが生成され、ディセーブルピンがHigh になります。プロセッサはGPIOでラッチ状態をクリアします。この回路は、セーフティクリティカルなアプリケーションにおいて、ソフトウェアをフォールトシャットダウンドープから外すために、あるいは単にプロセッサのオーバーヘッドを減らすために使用することができます。

GPIOが利用できないアプリケーションでは、TEMPピンを隣接するDIS2ピンに外部接続することができます。デバイスの温度が約135°Cに達すると、すべての出力が無効になり、モータが非通電になります。デバイスの温度が約95°C以下になると、SA53はモータを再起動します。TEMP端子のヒステリシスは、デバイスの寿命を大幅に縮める可能性のある熱振動の可能性を減らすために広く設定されています。

Figure 16: External Fault Latch Circuit

## 電圧不足ロックアウト

不足電圧ロックアウト条件は、VSが仕様表に示されたUVLO閾値を超えるまで、SA53が一方的にすべての出力FETを無効にするというものです。不足電圧ロックアウト条件が進行中であることを示す外部信号はありません。SA53のVS端子には、1相用と2相用の2つの端子があります。これらのピンの電源電圧は同じである必要はありませんが、どちらかがしきい値を下回った場合にUVLOが作動します。UVLO回路のヒステリシスは、一般的な電源変動による発振を防ぎます。

## 電流センス

SA53では、外部のパワーシャント抵抗は必要ありません。トップのPチャネル出力FETの順方向電流を測定し、それぞれの電流センス出力端子Ia、Ib、Icにミラーリングします。各電流センス端子とグランドなどの基準との間に抵抗を接続すると、抵抗にはその相の出力電流に比例した電圧が発生します。ADCは、これらの抵抗器の電圧を監視して保護したり、アプリケーション構成によっては閉ループのトルク制御を行うことができます。電流検出ピンは、VDD電源から電流を供給します。電流センス回路に必要なヘッドルームは約0.5Vです。各比例出力電流の公称スケールファクターは、本データシートの8ページにある代表的な性能プロットに示されています。

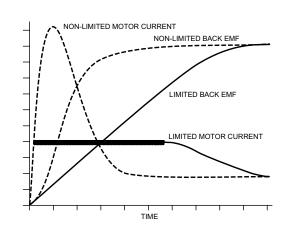

Figure 17: Start-Up Voltage and Current

## サイクルバイサイクル電流制限

モータの電流を直接制御できないアプリケーションでは、適切なアンプを選択する際に、モータの平均定格電流と突入電流の両方を考慮する必要があります。例えば、連続電流が1Aのモーターでは、起動時の突入条件に耐えるために、10Aをはるかに超えるピーク電流を供給できるドライブアンプが必要となる場合があります。

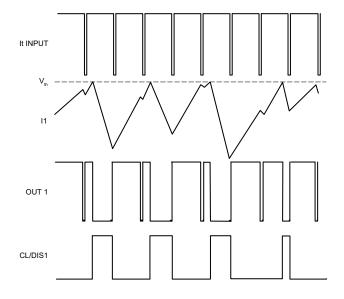

各上段出力FETの出力電流が測定されるため、SA53は非常に強固な電流制限スキームを提供することができます。これにより、SA53はほぼすべてのDCブラシモーターをスタートアップの突入条件で安全かつ容易に駆動することができます。電流が制限されると、始動トルクと加速度も制限されます。図17のプロットは、電流制限を有効にした場合としなかった場合の始動電流と逆起電力を示しています。2本の電流センスピンのいずれかの電圧が電流制限のしきい値電圧(Vth)を超えた場合、すべての出力が無効になります。すべての電流センスピンの電圧がVthスレッショルド電圧を下回り、問題のある相のトップサイド入力がLowになった後、トップサイド入力コマンド信号(1tまたは2t)の立ち上がりで、出力段はアクティブ状態に戻ります。ほとんどの整流方式では、電流制限はpwmサイクルごとにリセットされます。この方式では、以下のタイミング図に示すように、各pwmサイクル中に各相のピーク電流を規制します。平均電流とピーク電流の比率は、モーター巻線のインダクタンス、モーターに発生する逆起電力、およびパルスの幅に依存します。

図18は、電流制限のトリガーとリセットのシーケンスを示しています。いずれかの電流センス端子がVthを超えると、電流制限が働き、CL/DIS1がHighになります。電流センス信号がVthスレッショルドを超えた瞬間は、入力PWM信号とは非同期であることに注意してください。PWM周期とモーター巻線のL/R時定数との差により、サブサイクルオシレーションと呼ばれる耳障りなビート周波数が発生することがあります。

この発振は、図18のCL/DIS1端子の波形で確認できます。デューティサイクルが0%または100%の入力信号は、整流時以外は1tおよび2tの立ち上がりエッジがないため、電流制限機能と相容れない場合があります。高回転時には、パフォーマンスが低下する可能性があります。低回転では、電流リミットがトリップし、電流リミットラッチをリセットする整流エッジがないままモーター電流がゼロになると、モーターがストールする可能性があります。

電流制限機能は、CL/Dis1ピンをGNDに接続することで無効にすることができます。電流センスピンは、トップFETの出力電流情報を提供し続けます。

通常、電流センスピンは、電流制限コンパレータに電圧を供給する接地された抵抗に電流を供給します。電流制限抵抗を電圧出力DACに接続すれば、システムコントローラから電流制限を動的に制御することができます。これにより、電流制限のしきい値電圧を(Vth-VDAC)に下げることができます。起動時や反転時など、高いトルクが要求される状況が予想される場合、DACは電流制限を動的に調整し、高電流の期間を可能にします。低電流が予想される非定常動作時には、DAC出力電圧を上昇させて電流制限設定値を下げ、より保守的な故障保護を行うことができます。

Figure 18: Current Limit Waveforms

#### 外部フライバックダイオード

外付けフライバックダイオードは、内部のバックボディダイオードよりも優れた逆回復特性と低い順方向電圧降下を提供することになる。大電流アプリケーションでは、外付けフライバックダイオードは、モーター電流の整流時の電力損失と加熱を減らすことができます。これらのダイオードを選択する際に考慮すべき最も重要なパラメータは、逆回復時間とキャパシタンスです。超高速整流器は逆回復時間に優れ、ショットキーダイオードは一般的に低キャパシタンスです。これらのダイオードの必要性を判断し、最適なコンポーネントを選択するには、個々のアプリケーションの要件が指針となります。

Figure 19: Schottky Diodes

## 電力消費量

SA53の熱強化パッケージでは、3つの出力段で消費される電力を管理するために、いくつかのオプションが用意されています。従来のPWMアプリケーションにおける電力損失は、出力電力損失とスイッチング損失の組み合わせです。出力電力損失は、動作の象限と、逆電流または整流電流を流すために外付けのフライバック・ダイオードを使用するかどうかによって異なります。スイッチング損失は、典型的な性能グラフにあるように、PWMサイクルの周波数に依存します。

Figure 20: Timing Diagrams

Figure 21: Output Response

### **PACKAGE OPTIONS**

| Part Number | Apex Package Style | Description         |

|-------------|--------------------|---------------------|

| SA53        | UH                 | 44-pin HSOP Slug Up |

## テクニカルヘルプが必要ですか?エイペックスサポートにご連絡ください。

Apex Microtechnology製品に関するご質問やお問い合わせは、北米のフリーダイヤル800-546-2739までお願いします。 メールでのお問い合わせは、apex.support@apexanalog.com。

海外のお客様は、お近くのエイペックス・マイクロテクノロジー社の営業担当者に連絡してサポートを依頼することもできます。お近くの販売代理店をお探しの場合は、www.apexanalog.com にアクセスしてください。

### 重要なお知らせ

Apex Microtechnology, Inc.は、この文書に記載されている内容の正確さを保証するためにあらゆる努力をしています。しかし、これらの情報は予告なしに変更されることがあり、いかなる種類の保証(明示または黙示)もなしに「現状のまま」提供されます。Apex Microtechnologyは、信頼性向上のため、本書に記載された仕様や製品を予告なく変更する権利を有します。この文書は、Apex Microtechnologyの所有物であり、この情報を提供することにより、Apex Microtechnologyは、特許、マスクワーク権、著作権、商標、企業秘密、その他の知的財産権に基づくライセンスを明示的にも黙示的にも許諾しません。Apex Microtechnologyは、ここに含まれる情報に関連する著作権を所有しており、Apex Microtechnologyの集積回路またはその他のApex Microtechnologyの製品に関して、お客様の組織内で使用する場合に限り、情報のコピーを作成することに同意します。この同意は、一般的な配布、広告または宣伝目的のための複製、あるいは再販目的の作品の作成など、その他の複製には適用されません。

Apex Microtechnologyの製品は、生命維持装置、自動車の安全性、セキュリティ装置、その他の重要な用途に使用される製品 に適した設計、認可、保証をしていません。このような用途の製品は、完全にお客様またはお客様のリスクで使用されるもの とします。

Apex Microtechnology、Apex、Apex Precision Powerは、Apex Microtechnolgy, Inc.の商標です。ここに記載されているその他の企業名は、それぞれの所有者の商標である可能性があります。

#### PACKAGE STYLE HU